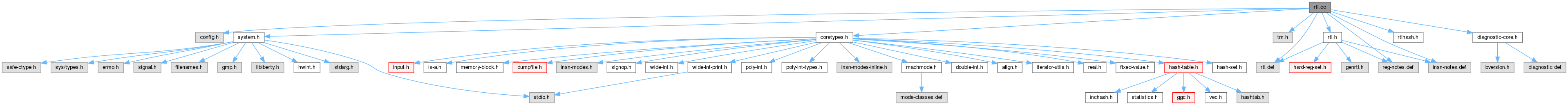

#include "config.h"#include "system.h"#include "coretypes.h"#include "tm.h"#include "rtl.h"#include "rtlhash.h"#include "diagnostic-core.h"#include "rtl.def"#include "insn-notes.def"#include "reg-notes.def"

Macros | |

| #define | DEF_RTL_EXPR(ENUM, NAME, FORMAT, CLASS) |

| #define | DEF_RTL_EXPR(ENUM, NAME, FORMAT, CLASS) |

| #define | DEF_RTL_EXPR(ENUM, NAME, FORMAT, CLASS) |

| #define | DEF_RTL_EXPR(ENUM, NAME, FORMAT, CLASS) |

| #define | RTX_CODE_HWINT_P_1(ENUM) |

| #define | RTX_CODE_HWINT_P RTX_CODE_HWINT_P_1 |

| #define | DEF_RTL_EXPR(ENUM, NAME, FORMAT, CLASS) |

| #define | DEF_INSN_NOTE(NAME) |

| #define | INSN_NOTE(NAME) |

| #define | DEF_REG_NOTE(NAME) |

| #define | REG_NOTE(NAME) |

Functions | |

| rtvec | rtvec_alloc (size_t n) |

| rtvec | shallow_copy_rtvec (rtvec vec) |

| unsigned int | rtx_size (const_rtx x) |

| rtx | rtx_alloc_stat_v (RTX_CODE code MEM_STAT_DECL, int extra) |

| rtx | rtx_alloc (RTX_CODE code MEM_STAT_DECL) |

| void | cwi_output_hex (FILE *outfile, const_rtx x) |

| bool | shared_const_p (const_rtx orig) |

| rtx | copy_rtx (rtx orig) |

| rtx | shallow_copy_rtx (const_rtx orig MEM_STAT_DECL) |

| bool | rtx_equal_p (const_rtx x, const_rtx y, rtx_equal_p_callback_function cb) |

| bool | rtvec_all_equal_p (const_rtvec vec) |

| bool | rtvec_series_p (rtvec vec, int start) |

| enum rtx_code | classify_insn (rtx x) |

| static int | rtx_count_cmp (const void *p1, const void *p2) |

| void | dump_rtx_statistics (void) |

Variables | |

| const unsigned char | rtx_length [NUM_RTX_CODE] |

| const char *const | rtx_name [NUM_RTX_CODE] |

| const char *const | rtx_format [NUM_RTX_CODE] |

| enum rtx_class | rtx_class [NUM_RTX_CODE] |

| const unsigned char | rtx_code_size [NUM_RTX_CODE] |

| const char *const | note_insn_name [NOTE_INSN_MAX] |

| const char *const | reg_note_name [REG_NOTE_MAX] |

| static size_t | rtx_alloc_counts [(int) LAST_AND_UNUSED_RTX_CODE] |

| static size_t | rtx_alloc_sizes [(int) LAST_AND_UNUSED_RTX_CODE] |

| static size_t | rtvec_alloc_counts |

| static size_t | rtvec_alloc_sizes |

| int | generating_concat_p |

| int | currently_expanding_to_rtl |

Macro Definition Documentation

◆ DEF_INSN_NOTE

| #define DEF_INSN_NOTE | ( | NAME | ) |

◆ DEF_REG_NOTE

| #define DEF_REG_NOTE | ( | NAME | ) |

◆ DEF_RTL_EXPR [1/5]

RTL utility routines. Copyright (C) 1987-2026 Free Software Foundation, Inc. This file is part of GCC. GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version. GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see <http://www.gnu.org/licenses/>.

This file is compiled twice: once for the generator programs once for the compiler.

Indexed by rtx code, gives number of operands for an rtx with that code. Does NOT include rtx header data (code and links).

Indexed by rtx code, gives the name of that kind of rtx, as a C string.

◆ DEF_RTL_EXPR [2/5]

RTL utility routines. Copyright (C) 1987-2026 Free Software Foundation, Inc. This file is part of GCC. GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version. GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see <http://www.gnu.org/licenses/>.

This file is compiled twice: once for the generator programs once for the compiler.

Indexed by rtx code, gives number of operands for an rtx with that code. Does NOT include rtx header data (code and links).

Indexed by rtx code, gives the name of that kind of rtx, as a C string.

◆ DEF_RTL_EXPR [3/5]

RTL utility routines. Copyright (C) 1987-2026 Free Software Foundation, Inc. This file is part of GCC. GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version. GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see <http://www.gnu.org/licenses/>.

This file is compiled twice: once for the generator programs once for the compiler.

Indexed by rtx code, gives number of operands for an rtx with that code. Does NOT include rtx header data (code and links).

Indexed by rtx code, gives the name of that kind of rtx, as a C string.

◆ DEF_RTL_EXPR [4/5]

RTL utility routines. Copyright (C) 1987-2026 Free Software Foundation, Inc. This file is part of GCC. GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version. GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see <http://www.gnu.org/licenses/>.

This file is compiled twice: once for the generator programs once for the compiler.

Indexed by rtx code, gives number of operands for an rtx with that code. Does NOT include rtx header data (code and links).

Indexed by rtx code, gives the name of that kind of rtx, as a C string.

◆ DEF_RTL_EXPR [5/5]

RTL utility routines. Copyright (C) 1987-2026 Free Software Foundation, Inc. This file is part of GCC. GCC is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 3, or (at your option) any later version. GCC is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. You should have received a copy of the GNU General Public License along with GCC; see the file COPYING3. If not see <http://www.gnu.org/licenses/>.

This file is compiled twice: once for the generator programs once for the compiler.

Indexed by rtx code, gives number of operands for an rtx with that code. Does NOT include rtx header data (code and links).

Indexed by rtx code, gives the name of that kind of rtx, as a C string.

◆ INSN_NOTE

| #define INSN_NOTE | ( | NAME | ) |

◆ REG_NOTE

| #define REG_NOTE | ( | NAME | ) |

◆ RTX_CODE_HWINT_P

| #define RTX_CODE_HWINT_P RTX_CODE_HWINT_P_1 |

◆ RTX_CODE_HWINT_P_1

| #define RTX_CODE_HWINT_P_1 | ( | ENUM | ) |

Function Documentation

◆ classify_insn()

Return an indication of which type of insn should have X as a body. In generator files, this can be UNKNOWN if the answer is only known at (GCC) runtime. Otherwise the value is CODE_LABEL, INSN, CALL_INSN or JUMP_INSN.

References ANY_RETURN_P, ASM_OPERANDS_LABEL_LENGTH, GET_CODE, LABEL_P, MATCH_OPERAND, MATCH_OPERATOR, MATCH_PARALLEL, SET, SET_DEST, SET_SRC, XVECEXP, and XVECLEN.

Referenced by emit(), and get_emit_function().

◆ copy_rtx()

Create a new copy of an rtx. Recursively copies the operands of the rtx, except for those few rtx codes that are sharable.

References CASE_CONST_ANY, copy_rtx(), gcc_unreachable, GET_CODE, GET_RTX_FORMAT, GET_RTX_LENGTH, i, NULL, ORIGINAL_REGNO, REG_P, REGNO, rtvec_alloc(), RTX_CODE, shallow_copy_rtx(), shared_const_p(), XEXP, XVEC, XVECEXP, and XVECLEN.

Referenced by add_equal_note(), add_store_equivs(), adjust_address_1(), adjust_cleared_regs(), analyze_insn_to_expand_var(), insn_propagation::apply_to_rvalue_1(), assign_parm_adjust_entry_rtl(), assign_parm_setup_block(), assign_parm_setup_reg(), assign_parm_setup_stack(), canon_reg_for_combine(), combine_instructions(), combine_reg_notes(), combine_simplify_rtx(), combine_var_copies_in_loop_exit(), cond_exec_process_insns(), confirm_change_group(), copy_delay_slot_insn(), copy_rtx(), cprop_jump(), cse_insn(), cse_process_note_1(), curr_insn_transform(), doloop_modify(), doloop_optimize(), eliminate_partially_redundant_load(), eliminate_regs_1(), emit_libcall_block_1(), emit_library_call_value_1(), emit_move_insn(), equiv_can_be_consumed_p(), expand_absneg_bit(), expand_binop(), expand_debug_expr(), expand_debug_parm_decl(), expand_DIVMOD(), expand_expr_real_1(), expand_expr_real_2(), expand_field_assignment(), expand_fix(), expand_operands(), filter_notes(), find_cond_trap(), find_reloads_address(), find_shift_sequence(), pair_fusion::find_trailing_add(), fold_rtx(), force_const_mem(), forward_propagate_and_simplify(), pair_fusion_bb_info::fuse_pair(), get_arg_pointer_save_area(), get_last_value(), get_secondary_mem(), get_stored_val(), if_then_else_cond(), inherit_in_ebb(), init_eliminable_invariants(), insert_base_initialization(), insert_part_to_rtx_on_edge(), insert_partition_copy_on_edge(), insert_restore(), insert_rtx_to_part_on_edge(), insert_save(), insert_set_in_table(), insert_store(), insert_temp_slot_address(), insert_value_copy_on_edge(), instantiate_virtual_regs_in_insn(), inv_can_prop_to_addr_use(), ira_update_equiv_info_by_shuffle_insn(), iv_number_of_iterations(), load_register_parameters(), lra_constraints(), lra_copy_reg_equiv(), lra_init_equiv(), make_memloc(), match_asm_constraints_1(), match_reload(), maybe_legitimize_operands(), noce_convert_multiple_sets_1(), noce_emit_all_but_last(), noce_try_cmove_arith(), noce_try_cond_arith(), plus_constant(), process_addr_reg(), process_address_1(), process_insert_insn(), process_one_cond_exec(), process_rtx(), process_substs_on_one_elem(), propagate_for_debug_subst(), record_value_for_reg(), remove_pseudos(), replace_label(), replace_reg_with_saved_mem(), resolve_debug(), resolve_operand_for_swap_move_operator(), resolve_shift_zext(), resolve_simple_move(), save_call_clobbered_regs(), simplify_context::simplify_binary_operation_1(), simplify_if_then_else(), simplify_context::simplify_relational_operation_1(), simplify_replace_fn_rtx(), split_insn(), split_iv(), store_constructor(), store_constructor_field(), store_field(), store_fixed_bit_field_1(), store_one_arg(), subst(), subst_dup(), try_apply_stack_adjustment(), try_combine(), try_eliminate_compare(), try_fwprop_subst_pattern(), try_merge_compare(), try_replace_reg(), unroll_loop_runtime_iterations(), update_equiv_regs(), and update_ld_motion_stores().

◆ cwi_output_hex()

| void cwi_output_hex | ( | FILE * | outfile, |

| const_rtx | x ) |

Write the wide constant X to OUTFILE.

References CWI_ELT, CWI_GET_NUM_ELEM, gcc_assert, HOST_WIDE_INT_PRINT_HEX, HOST_WIDE_INT_PRINT_PADDED_HEX, and i.

Referenced by rtx_writer::print_rtx().

◆ dump_rtx_statistics()

| void dump_rtx_statistics | ( | void | ) |

References GET_RTX_NAME, i, LAST_AND_UNUSED_RTX_CODE, PRsa, rtvec_alloc_counts, rtvec_alloc_sizes, rtx_alloc_counts, rtx_alloc_sizes, rtx_count_cmp(), and SIZE_AMOUNT.

Referenced by dump_memory_report().

◆ rtvec_all_equal_p()

| bool rtvec_all_equal_p | ( | const_rtvec | vec | ) |

Return true if all elements of VEC are equal.

References CASE_CONST_UNIQUE, GET_CODE, GET_NUM_ELEM, i, RTVEC_ELT, and rtx_equal_p().

Referenced by gen_rtx_CONST_VECTOR().

◆ rtvec_alloc()

| rtvec rtvec_alloc | ( | size_t | n | ) |

Allocate an rtx vector of N elements. Store the length, and initialize all elements to zero.

References rtvec_def::elem, gcc_assert, ggc_alloc_rtvec_sized, INT_MAX, PUT_NUM_ELEM, rtvec_alloc_counts, and rtvec_alloc_sizes.

Referenced by add_attributes(), adjust_insn(), alter_attrs_for_insn(), rtx_vector_builder::build(), cleanup_auto_inc_dec(), convert_set_attr(), convert_set_attr_alternative(), copy_insn_1(), copy_rtx(), md_reader::copy_rtx_for_iterators(), cselib_expand_value_rtx_1(), decompose_register(), emit_delay_sequence(), emit_group_load_into_temps(), emit_group_move_into_temps(), expand_asm_loc(), expand_asm_memory_blockage(), expand_asm_reg_clobber_mem_blockage(), expand_asm_stmt(), expand_debug_expr(), expand_delays(), expand_vector_broadcast(), gen_mnemonic_setattr(), gen_rewrite_sequence(), gen_rtvec(), gen_rtvec_v(), gen_rtvec_v(), get_peephole2_pattern(), insn_invalid_p(), instantiate_virtual_regs_in_insn(), ira_nullify_asm_goto(), main(), make_automaton_attrs(), make_canonical(), process_one_cond_exec(), process_rtx(), process_substs_on_one_elem(), rtx_reader::read_rtx_operand(), recog_for_combine_1(), remove_clobbers(), replace_operands_with_dups(), replace_reg_with_saved_mem(), shallow_copy_rtvec(), simplify_context::simplify_binary_operation_1(), simplify_cond(), simplify_const_binary_operation(), simplify_context::simplify_ternary_operation(), store_constructor(), substitute_address(), try_combine(), try_eliminate_compare(), verify_changes(), and vt_add_function_parameter().

◆ rtvec_series_p()

Return true if VEC contains a linear series of integers

{ START, START+1, START+2, ... }.

References CONST_INT_P, GET_NUM_ELEM, i, INTVAL, and RTVEC_ELT.

Referenced by vec_series_highpart_p(), and vec_series_lowpart_p().

◆ rtx_alloc()

Allocate an rtx of code CODE. The CODE is stored in the rtx; all the rest is initialized to zero.

References MEM_STAT_DECL, PASS_MEM_STAT, rtx_alloc_stat_v(), and RTX_CODE.

Referenced by add_attributes(), add_define_attr(), add_implicit_parallel(), add_mode_tests(), alter_attrs_for_insn(), attr_rtx_1(), const_double_from_real_value(), const_fixed_from_fixed_value(), convert_set_attr(), convert_set_attr_alternative(), md_reader::copy_rtx_for_iterators(), emit_barrier(), emit_barrier_after(), emit_barrier_before(), emit_jump_table_data(), expand_delays(), gen_mnemonic_setattr(), gen_raw_REG(), gen_rtx_CONST_INT(), generate_match_dup(), get_peephole2_pattern(), immed_double_const(), init_expr_target(), main(), make_automaton_attrs(), make_call_insn_raw(), make_canonical(), make_debug_insn_raw(), make_insn_raw(), make_jump_insn_raw(), make_note_raw(), modify_attr_enabled_ce(), process_one_cond_exec(), process_rtx(), rtx_reader::read_rtx_code(), rtx_reader::read_rtx_variadic(), remove_clobbers(), replace_operands_with_dups(), rtx_reader::rtx_alloc_for_name(), simplify_cond(), substitute_address(), and write_predicate_subfunction().

◆ rtx_alloc_stat_v()

Allocate an rtx of code CODE with EXTRA bytes in it. The CODE is stored in the rtx; all the rest is initialized to zero.

References ggc_alloc_rtx_def_stat(), MEM_STAT_DECL, PASS_MEM_STAT, rtx_alloc_counts, rtx_alloc_sizes, RTX_CODE, RTX_CODE_SIZE, and rtx_init().

Referenced by rtx_alloc().

◆ rtx_count_cmp()

|

static |

Comparator of indices based on rtx_alloc_counts.

References rtx_alloc_counts.

Referenced by dump_rtx_statistics().

◆ rtx_equal_p()

| bool rtx_equal_p | ( | const_rtx | x, |

| const_rtx | y, | ||

| rtx_equal_p_callback_function | cb ) |

Return true if X and Y are identical-looking rtx's. This is the Lisp function EQUAL for rtx arguments. Call CB on each pair of rtx if CB is not NULL. When the callback returns true, we continue with the new pair.

References CASE_CONST_UNIQUE, DEBUG_IMPLICIT_PTR_DECL, DEBUG_PARAMETER_REF_DECL, ENTRY_VALUE_EXP, gcc_unreachable, GET_CODE, GET_MODE, GET_RTX_FORMAT, GET_RTX_LENGTH, i, label_ref_label(), MEM_ADDR_SPACE, NULL, REGNO, rtx_equal_p(), same_vector_encodings_p(), SUBREG_BYTE, XEXP, XINT, XLOC, XSTR, XVECEXP, XVECLEN, XWINT, and y.

Referenced by add_equal_note(), add_var_loc_to_decl(), allocate_dynamic_stack_space(), analyze_insn_to_expand_var(), apply_distributive_law(), insn_propagation::apply_to_rvalue_1(), assign_call_lhs(), attr_equal_p(), base_alias_check(), bbs_ok_for_cmove_arith(), find_comparison_dom_walker::before_dom_children(), builtin_memset_gen_str(), calculate_needs_all_insns(), can_combine_p(), can_eliminate_compare(), can_replace_by(), canon_reg_for_combine(), canonicalize_condition(), canonicalize_insn(), change_address_1(), check_and_make_def_conflict(), choose_reload_regs(), clobber_slot_part(), combinable_i3pat(), combine_reloads(), combine_simplify_rtx(), compare_and_jump_seq(), cond_move_process_if_block(), condition_dominates_p(), const_vec_series_p_1(), copy_frame_info_to_split_insn(), copyprop_hardreg_forward_1(), count_occurrences(), cprop_jump(), cse_cc_succs(), cse_insn(), cselib_record_sets(), decompose_automod_address(), delegitimize_mem_from_attrs(), delete_address_reloads(), delete_address_reloads_1(), delete_output_reload(), delete_slot_part(), df_find_single_def_src(), distribute_notes(), do_compare_rtx_and_jump(), do_input_reload(), do_output_reload(), doloop_condition_get(), dw_val_equal_p(), address_reload_context::emit_autoinc(), emit_block_cmp_via_loop(), emit_block_move_hints(), emit_conditional_move(), emit_conditional_move_1(), emit_group_store(), emit_input_reload_insns(), emit_move_insn(), emit_note_insn_var_location(), emit_output_reload_insns(), emit_store_flag_int(), addr_hasher::equal(), const_rtx_desc_hasher::equal(), invariant_group_base_hasher::equal(), equal_different_set_p(), rtx_vector_builder::equal_p(), expand_binop(), expand_call(), expand_rotate_as_vec_perm(), expand_strided_load_optab_fn(), expand_vec_perm_1(), expand_vec_perm_const(), extract_ashift_operands_p(), extract_writebacks(), fill_slots_from_thread(), find_address(), find_args_size_adjust(), find_auto_inc(), find_call_crossed_cheap_reg(), find_equiv_reg(), find_inc(), find_loc_in_1pdv(), find_reg_fusage(), find_reloads(), find_reloads_address(), find_reloads_address_1(), find_reloads_subreg_address(), find_reloads_toplev(), find_src_set_src(), fixup_debug_uses_trailing_add(), fold_rtx(), force_reg(), free_load_extend(), gcse_emit_move_after(), gen_reload(), get_biv_step_1(), get_hard_reg_initial_reg(), get_init_value(), get_reload_reg(), if_then_else_cond(), immune_p(), implies_p(), init_alias_analysis(), insns_have_identical_cfa_notes(), invariant_eq_p(), invariant_expr_equal_p(), ira_setup_alts(), ira_update_equiv_info_by_shuffle_insn(), iv_number_of_iterations(), kill_set_value(), known_cond(), lra_emit_move(), make_compound_operation_int(), mark_referenced_resources(), match_asm_constraints_1(), match_plus_neg_pattern(), maybe_legitimize_operands(), maybe_propagate_label_ref(), maybe_swap_commutative_operands(), merge_notes(), move2add_use_add3_insn(), negated_ops_p(), noce_get_alt_condition(), noce_try_abs(), noce_try_addcc(), noce_try_bitop(), noce_try_cmove_arith(), noce_try_cond_arith(), noce_try_minmax(), noce_try_move(), noce_try_store_flag_constants(), noce_try_store_flag_mask(), nonoverlapping_memrefs_p(), old_insns_match_p(), outgoing_edges_match(), pair_mem_strip_offset(), parse_add_or_inc(), prepare_cmp_insn(), propagate_for_debug_subst(), push_reg_equiv_alt_mem(), push_reload(), record_jump_cond(), record_reg_classes(), record_store(), redundant_insn(), reg_mentioned_p(), reg_overlap_mentioned_for_reload_p(), relax_delay_slots(), reload_combine_note_use(), reload_combine_recognize_const_pattern(), reload_combine_recognize_pattern(), reload_cse_move2add(), reload_cse_regs_1(), reload_reg_free_for_value_p(), reloads_unique_chain_p(), reversed_comparison_code_parts(), rtvec_all_equal_p(), rtx_equal_for_cselib_1(), rtx_equal_for_field_assignment_p(), rtx_equal_for_memref_p(), rtx_equal_p(), rtx_interchangeable_p(), rtx_referenced_p(), rtx_renumbered_equal_p(), safe_from_p(), same_dw_val_p(), set_noop_p(), set_of_1(), set_slot_part(), setup_reg_equiv(), simplify_context::simplify_binary_operation_1(), simplify_comparison(), simplify_context::simplify_cond_clz_ctz(), simplify_const_relational_operation(), simplify_context::simplify_distributive_operation(), simplify_if_then_else(), simplify_context::simplify_ior_with_common_term(), simplify_context::simplify_logical_relational_operation(), simplify_context::simplify_merge_mask(), simplify_context::simplify_relational_operation_1(), simplify_replace_fn_rtx(), simplify_rotate_op(), simplify_rtx(), simplify_set(), simplify_shift_const_1(), simplify_context::simplify_ternary_operation(), simplify_context::simplify_unary_operation_1(), simplify_using_condition(), sp_based_mem_offset(), split_insn(), store_constructor(), store_expr(), subst_reg_equivs(), substitute(), swap_commutative_operands_with_target(), thread_jump(), try_back_substitute_reg(), try_combine(), try_eliminate_compare(), try_merge_delay_insns(), try_replace_in_use(), try_replace_reg(), try_split(), update_equiv_regs(), update_temp_slot_address(), use_related_value(), valid_replacement_for_asm_input_p_1(), validate_change_1(), validate_replace_rtx_1(), validate_simplify_insn(), values_equal_p(), variable_part_different_p(), and variable_union().

◆ rtx_size()

| unsigned int rtx_size | ( | const_rtx | x | ) |

Return the number of bytes occupied by rtx value X.

References CONST_POLY_INT_COEFFS, CONST_POLY_INT_P, CONST_WIDE_INT_NUNITS, CONST_WIDE_INT_P, GET_CODE, RTX_CODE_SIZE, RTX_HDR_SIZE, and SYMBOL_REF_HAS_BLOCK_INFO_P.

Referenced by shallow_copy_rtx().

◆ shallow_copy_rtvec()

Create a bitwise copy of VEC.

References rtvec_def::elem, GET_NUM_ELEM, and rtvec_alloc().

Referenced by cselib_subst_to_values(), and simplify_replace_fn_rtx().

◆ shallow_copy_rtx()

Create a new copy of an rtx. Only copy just one level.

References CASE_CONST_ANY, GET_CODE, ggc_alloc_rtx_def_stat(), INSN_P, MEM_STAT_DECL, PASS_MEM_STAT, RTX_FLAG, and rtx_size().

Referenced by add_uses(), adjust_insn(), cleanup_auto_inc_dec(), convert_debug_memory_address(), convert_memory_address_addr_space_1(), copy_insn_1(), copy_rtx(), copy_rtx_if_shared_1(), cselib_expand_value_rtx_1(), cselib_subst_to_values(), eliminate_regs_1(), emit_block_move_hints(), expand_assignment(), expand_debug_expr(), find_reloads_toplev(), lra_eliminate_regs_1(), new_cselib_val(), optimize_bitfield_assignment_op(), replace_operands_with_dups(), replace_read(), and simplify_replace_fn_rtx().

◆ shared_const_p()

Return true if ORIG is a sharable CONST.

References gcc_assert, GET_CODE, block_symbol::offset, poly_int_rtx_p(), and XEXP.

Referenced by cleanup_auto_inc_dec(), copy_insn_1(), copy_rtx(), copy_rtx_if_shared_1(), cprop_constant_p(), cselib_expand_value_rtx_1(), plus_constant(), and verify_rtx_sharing().

Variable Documentation

◆ currently_expanding_to_rtl

| int currently_expanding_to_rtl |

Nonzero when we are expanding trees to RTL.

Referenced by gimple_outgoing_range::calc_switch_ranges(), commit_edge_insertions(), commit_one_edge_insertion(), expand_expr_real_1(), flush_mark_addressable_queue(), gimple_assign_rhs_to_tree(), mark_addressable_1(), patch_jump_insn(), fold_using_range::range_of_range_op(), and redirect_branch_edge().

◆ generating_concat_p

| int generating_concat_p |

Nonzero when we are generating CONCATs.

Referenced by assign_parm_setup_block(), avoid_likely_spilled_reg(), expand_asm_stmt(), expand_function_end(), gen_reg_rtx(), pop_function_context(), and prepare_function_start().

◆ note_insn_name

| const char* const note_insn_name[NOTE_INSN_MAX] |

Names for kinds of NOTEs and REG_NOTEs.

◆ reg_note_name

| const char* const reg_note_name[REG_NOTE_MAX] |

Names for REG_NOTE's in EXPR_LIST insn's.

◆ rtvec_alloc_counts

|

static |

Referenced by dump_rtx_statistics(), and rtvec_alloc().

◆ rtvec_alloc_sizes

|

static |

Referenced by dump_rtx_statistics(), and rtvec_alloc().

◆ rtx_alloc_counts

|

static |

Referenced by dump_rtx_statistics(), rtx_alloc_stat_v(), and rtx_count_cmp().

◆ rtx_alloc_sizes

|

static |

Referenced by dump_rtx_statistics(), and rtx_alloc_stat_v().

◆ rtx_class

| enum rtx_class rtx_class[NUM_RTX_CODE] |

Indexed by rtx code, gives a character representing the "class" of that rtx code. See rtl.def for documentation on the defined classes.

◆ rtx_code_size

| const unsigned char rtx_code_size[NUM_RTX_CODE] |

Indexed by rtx code, gives the size of the rtx in bytes.

◆ rtx_format

| const char* const rtx_format[NUM_RTX_CODE] |

Indexed by rtx code, gives a sequence of operand-types for rtx's of that code. The sequence is a C string in which each character describes one operand.

◆ rtx_length

| const unsigned char rtx_length[NUM_RTX_CODE] |

◆ rtx_name

| const char* const rtx_name[NUM_RTX_CODE] |